Developed based on AMD/Xilinx 10G Ethernet MAC IP, MTU data transmission up to 9000 bytes, AXI4 stream interface, supporting Kintex™ 7 / Virtex™ 7 / UltraScale™ / Ultrade+™ / Zynq UltraScale+™ Series FPGA devices, high bandwidth and low latency, fast data transmission and real-time processing, accurate and efficient data transmission of TCP protocol stack.

In stock:

>9, ready to ship in 2 workdays

Developed based on AMD/Xilinx 10G Ethernet MAC IP, MTU supports up to 9000 bytes of data transmission, standard AXI4 Stream interface, supports AMD/Xilinx Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC, Virtex UltraScale+, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Kintex UltraScale, Virtex 7, Kintex 7, Zynq 7030/7035/7045/7100 Series FPGA devices. The 10G Ethernet with high bandwidth and low latency ensures fast data transmission and real-time processing, while the TCP protocol stack further improves the efficiency and accuracy of data transmission.

We provide you with a fast, reliable, low-cost, and high-performance solution that significantly shortens the time to market and is suitable for high bandwidth, low latency, and high-speed data transmission scenarios.

● Data Center

● Cloud Computing Storage

● Telecommunications

● Industrial Automation

● Internet of Things

● Medical

● 4K/8K HD Video Transmission

● Scientific Research Experiment

● Test Measurement

● Implement an ARP/IPV4/ICMP/TCP protocol stack that complies with the IEEE802.3 standard based on the OSI layered model.

● Supports ARP for obtaining or sending MAC addresses.

● Supports ICMP for responding to Ping commands.

● Acts as a TCP server, responding to client connection and disconnection requests, with the ability to actively initiate a disconnection request.

● ARP responds to all incoming requests but maintains only a single ARP table dedicated to active connections.

● Connection requests are not responding if the ARP table is not established.

● Connection requests are only accepted after receiving the configured TCP listen request when the ARP table is established.

● 10Gbps Ethernet connection, supporting TCP/IP checksum processing, calculating CRC by the MAC IP.

● Developed based on AMD/Xilinx 10G MAC IP, supporting MTU up to 9000 Bytes and a minimum 64 Bytes data transmission size.

● Handles sending, receiving, and responding of TCP data packets, and keeps maintenance on heartbeat messages.

● Ensures in-order delivery, retransmission, acknowledgment, and fast retransmission in TCP transmission.

● Flow control is based on receiving and sending windows in TCP transmission.

● After establishing a TCP connection, immediately disconnect upon receiving an RST packet from the client.

● Up to two TCP connections in maximum.

● AXI4 Stream interface for users, with the protocol stack using a clock of 156.25 MHz generated by the MAC IP, and a 10 Gbps data bus width of 64 bits.

● The internal data of the TCP/IP protocol stack IP core is processed with 8-byte alignment.

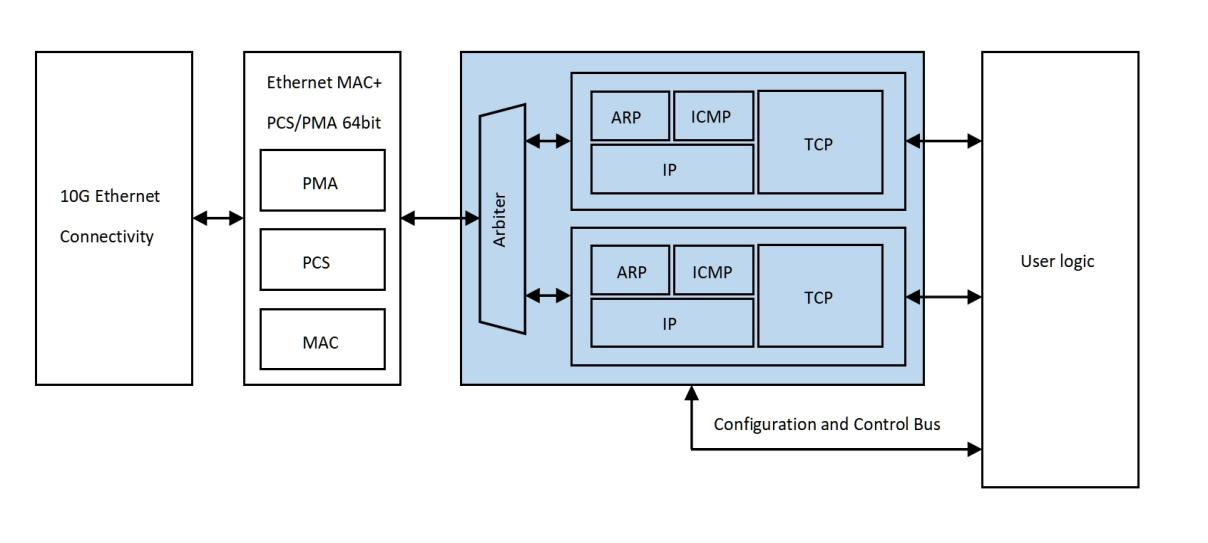

The diagram below shows the position of the 10G Ethernet TCP/IP Protocol Stack FPGA IP Core within the system design:

The 10G Ethernet TCP/IP Protocol Stack FPGA IP Core uses standard AXI4-Stream interfaces for both the user interface and the Ethernet MAC + PCS/PMA IP interface. The Ethernet MAC + PCS/PMA can be any third-party IP. In the provided design example, AMD/Xilinx 10G/25G Ethernet Subsystem IP is used.

The evaluation of IP resource consumption adopts AMD Kintex UltraScale XCKU040 series FPGA development board, which provides a fully functional design platform for building communication centric Ethernet applications. The Kintex UltraScale XCKU040 series FPGA development board provides an out of the box hardware platform with reference designs, which can shorten development time and allow you to focus on your target applications.

| Chip Model | Device Series | Frequency (MHz) | CLB Regs | CLB LUTs | CLB | BRAM Tile | Design Tools | |||

|---|---|---|---|---|---|---|---|---|---|---|

| XCKU040-FFVA1156-2-i | Kintex-UltraScale | 156.25 | 9689 | 9853 | 1989 | 82 | Vivado 2020.1 | |||

Note: Actual IP resource consumption is affected by the consumption of other logical resources during instantiation.

Please contact us for more details.

IP Information

Documentation

10G TCP/IP protocol stack IP Core User Guide

IP Provided Format

Encrypted Netlist

Design Language

Verilog

Development Tool

Vivado 2020.1

Supported Devices

AMD/Xilinx Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC, Virtex UltraScale+, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Kintex UltraScale, Virtex 7, Kintex 7, Zynq 7030/7035/7045/7100

Please contact us for more details.

Please contact us should you have any need.

10G TCP_IP protocol stack IP Core User Guide

2024-11-05